VGA(Video Graphics Array),视频图形阵列,是一种视频传输标准,具有分辨率高、显示速度快、颜色丰富等优点,不支持音频传输。

1.VGA简介

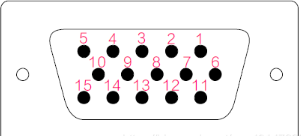

1.1 VGA接口

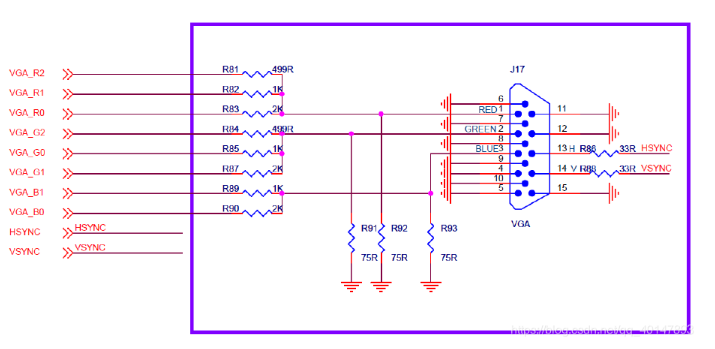

●VGA接口:

VGA是一种D型接口,采用非对称分布连接方式,共有15针,分三排,每排5个孔。

●VGA接口管脚表:

在15个管脚中,其中比较重要的是3根RGB彩色分量信号和2根扫描同步信号HSYNC和VSYNC。

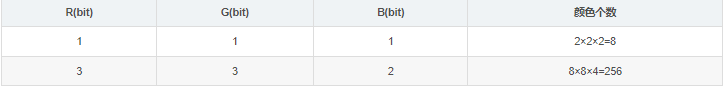

●像素点构成: VGA显示器上每一个像素点可以有多种颜色,由三基色信号R、G、B组合构成。如果每个像素点采用3位二进制数表示(R、G、B信号各1位),则总共可以显示2×2×2=8种颜色,每个像素点采用8位二进制数表示(R、G、B信号分别为3、3、2),则总共可以显示8×8×4=256种颜色。

R(bit) G(bit) B(bit) 颜色个数

1.2 VGA是如何实现显示的

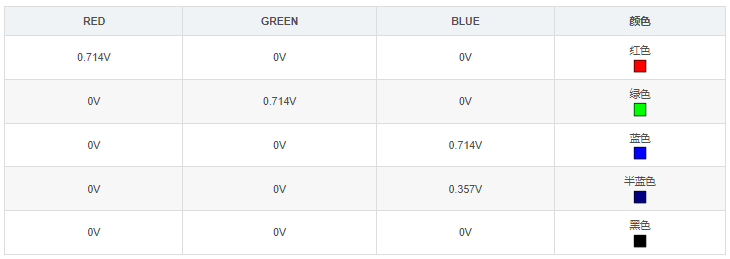

要知道VGA显示器是不认识数字信号的,它只认识模拟信号。所谓它只认识模拟信号,即 在它的数据引脚1、2、3(RED、GREEN、BLUE)输入的不是简单的0、1数字信号,而是模拟电压(0V-0.714V)。1、2、3引脚具有不同的电压时,VGA显示器显示不同的颜色。

但是FPGA要想产生模拟信号就需要借助DA,利用DA产生模拟信号,输出至VGA的RED、GREEN、BLUE基色数据线。也有利用电阻网络分流模拟DA实现的。

●VGA各种颜色如何实现的

在VGA接口的1、2、3引脚分别接至以下电压:

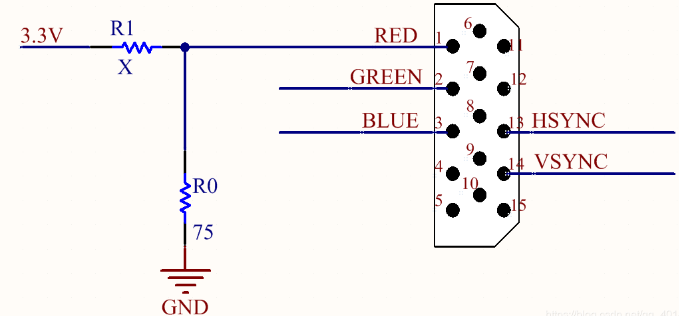

●利用电阻网络分流模拟DA

R-2R电阻网络分压原理:

(1)每个像素点采用3位二进制(R(1bit)、G(1bit)、B(1bit))

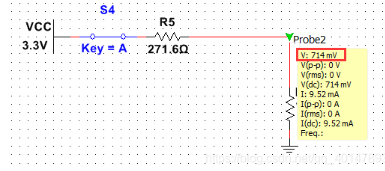

例如VGA显示器要显示纯红色,则在RED引脚要输入0.714V电压,如果我们VGA_RED信号为1位电路如下图所示,那么(X+75)/3.3=75/0.714,计算得出X=271.6。

将R1阻值选择为271.6Ω,仿真得出VGA_RED引脚输入电压确实为0.714V。

(2)每个像素点采用8位二进制(R(3bit)、G(3bit)、B(2bit))

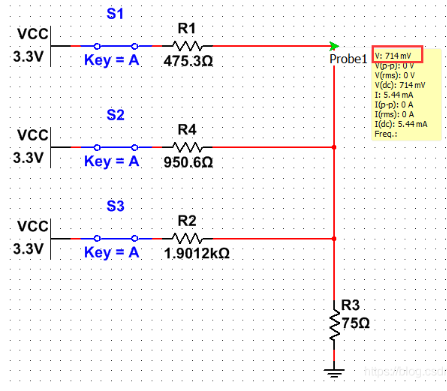

如果我们VGA_RED信号为3位电路如下图所示,那么(X+75)/3.3=75/0.714,计算得出X=271.6,X是通过三个电阻并联得到的。Rx||2Rx||4Rx=X,得出Rx=475.3Ω。

将R1、R2、R3阻值选择为475.3Ω、950.6Ω、1.9012KΩ,并且将R1、R2、R3都接通至3.3V,得出VGA_RED节点电压为0.714V。

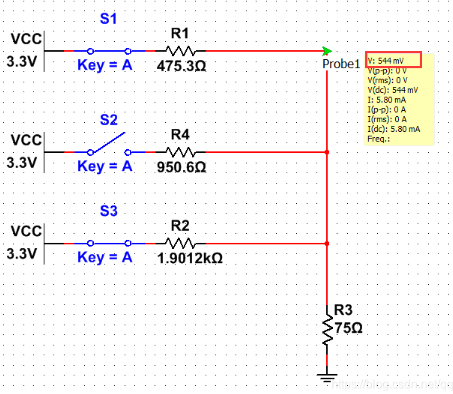

上图的三个3.3V节点接至FPGA的三个输出引脚,就可以通过数字量去控制模拟量了。 例如FPGA三引脚输出数字量101,则对应以下电路(则会对应不同的颜色),VGA_RED节点电压为0.554V:

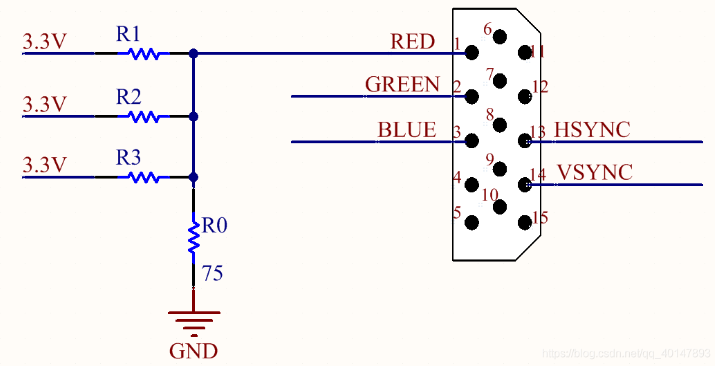

VGA_GREEN、VGA_BLUE同理,我们就会得到以下完整的电路:

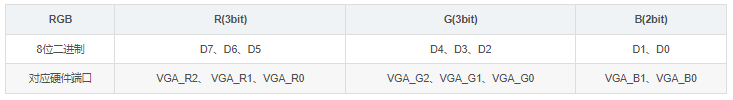

原理很简单,之前说过,每个像素点采用8位二进制数表示(R、G、B信号分别为3、3、2)。观察上图得到以下对应关系:

RGB R(3bit) G(3bit) B(2bit)

8位二进制 D7、D6、D5 D4、D3、D2 D1、D0

对应硬件端口 VGA_R2、 VGA_R1、VGA_R0 VGA_G2、VGA_G1、VGA_G0 VGA_B1、VGA_B0

D7-D0分别映射到FPGA的8个IO口,就可以通过这8个IO口的数字量去控制VGA的颜色显示了。

2. VGA通信协议

2.1 VGA通信时序

从上图中看出,帧时序和行时序都有四部分:

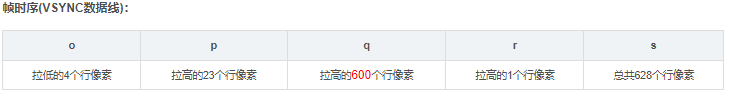

●帧时序:

帧时序的四个部分别是:同步脉冲(Sync o)、显示后沿(Back porch p)、显示时序段(Display interval q)和显示前沿(Front porchr)。其中同步脉冲(Sync o)、显示后沿(Back porch p)和显示前沿(Front porch r)是消隐区,RGB信号无效,屏幕不显示数据。显示时序段(Display interval q)是有效数据区。.

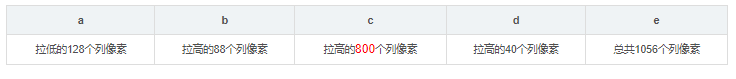

●行时序:

行时序的四个部分分别是:同步脉冲(Sync a)、显示后沿(Back porch b)、显示时序(Display interval c)和显示前沿(Front porchd)。其中同步脉冲(Sync a)、显示后沿(Back porch b)和显示前沿(Front porch d)是消隐区,RGB信号无效,屏幕不显示数据。显示时序段(Display interval c)是有效数据区。

2.2 VGA时序解析

不同的分辨率,它的时序是不一样的。例如800*600@60Hz的VGA时序:

行时序(HSYNC数据线):

3. FPGA驱动VGA显示彩条

电路图:

原文地址:http://www.cnblogs.com/54programer/p/16831874.html