功能

1. 单axi-stream 接口输入,axis输出。(10bit rbg输入,10bit rbg输出。输入为大分辨率,输出为小分辨率)

2. 使用xilinx hls 编写。

20221027 优化

3. 配置寄存器有

效果

输入图像 大分辨率

输出图像 小分辨率

支持

支持xilinx 所有系列fpga

仿真

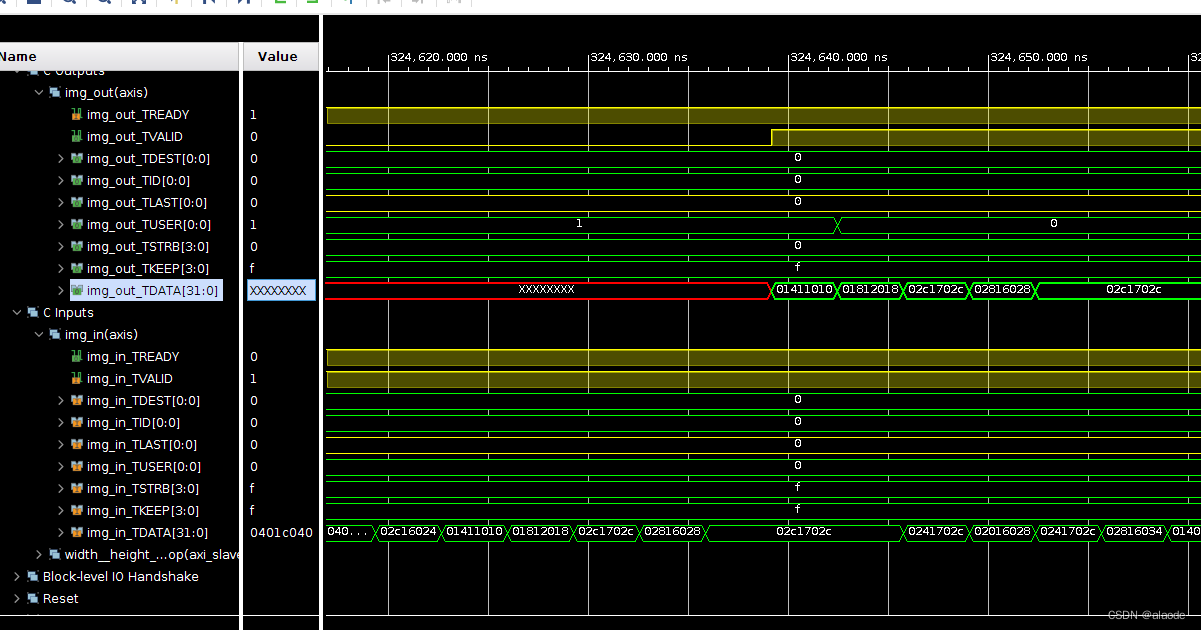

图像开始输出位置

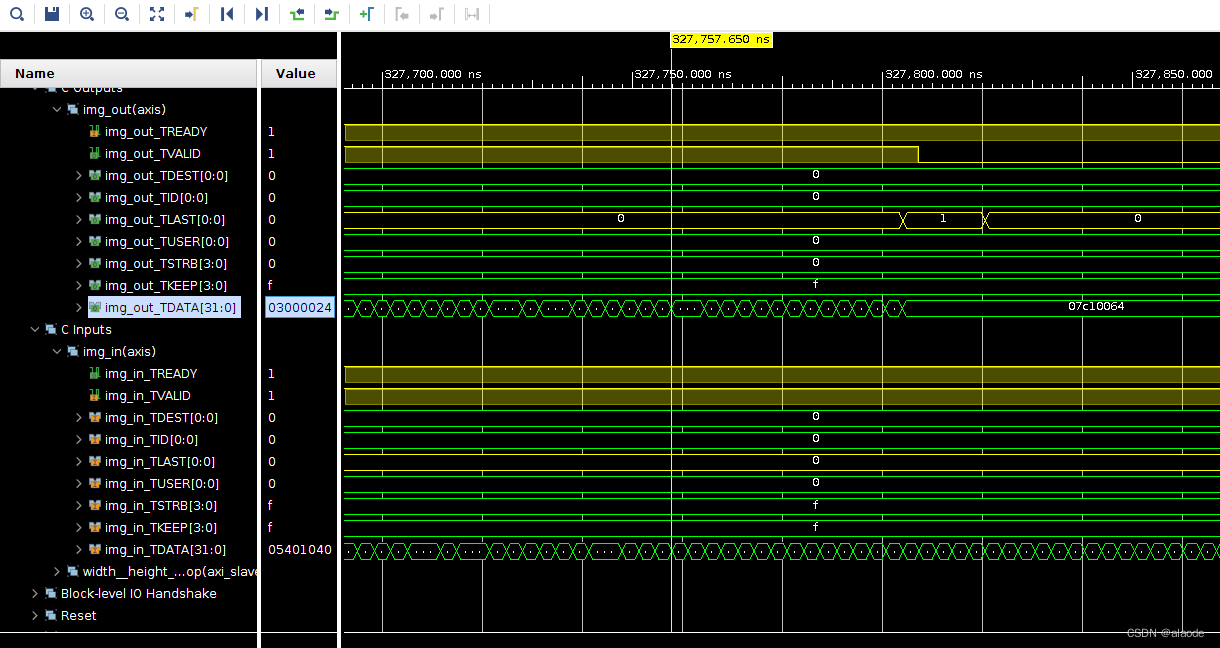

图像输出行结束

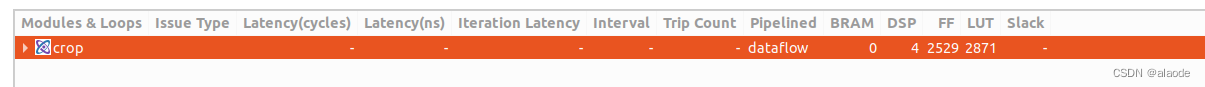

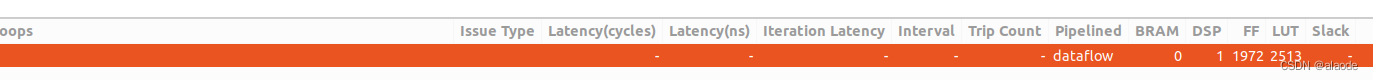

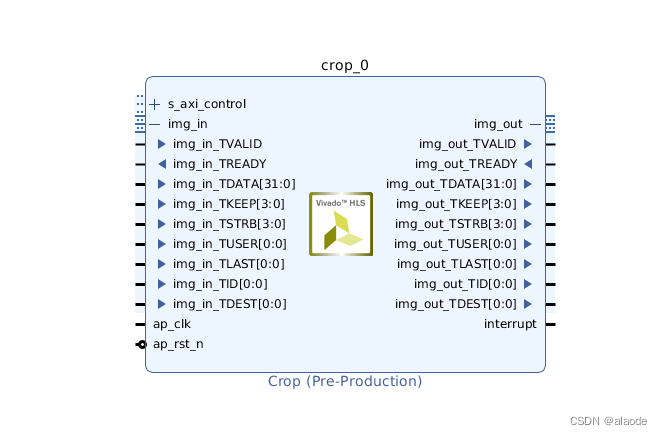

ip 接口

原文地址:http://www.cnblogs.com/alaode/p/16862421.html

1. 本站所有资源来源于用户上传和网络,如有侵权请邮件联系站长!

2. 分享目的仅供大家学习和交流,请务用于商业用途!

3. 如果你也有好源码或者教程,可以到用户中心发布,分享有积分奖励和额外收入!

4. 本站提供的源码、模板、插件等等其他资源,都不包含技术服务请大家谅解!

5. 如有链接无法下载、失效或广告,请联系管理员处理!

6. 本站资源售价只是赞助,收取费用仅维持本站的日常运营所需!

7. 如遇到加密压缩包,默认解压密码为"gltf",如遇到无法解压的请联系管理员!

8. 因为资源和程序源码均为可复制品,所以不支持任何理由的退款兑现,请斟酌后支付下载

声明:如果标题没有注明"已测试"或者"测试可用"等字样的资源源码均未经过站长测试.特别注意没有标注的源码不保证任何可用性