乒乓操作学习记录如下:

乒乓操作” 是一个常常应用于数据流控制的设计思想, 典型的乒乓操作方法如下图 所示: 乒乓操作的处理流程为:输入数据流通过“ 输入数据选择单元”将数据流等时分配到两个“数据缓冲模块”, 数据缓冲模块可以为任何存储模块,比较常用的存储单元为双口RAM (DPRAM)、单口RAM (SPRAM)、FIFO等。 在第2个缓冲周期, 通过“ 输入数据选择单元” 的切换, 将输入的数据流缓存到“ 数据缓冲模块2”,同时将“数据缓冲模块1”缓存的第1个周期数据通过“输入数据选择单元”的选择,送到“数据流运算处理模块” 进行运算处理。

乒乓操作最大的特点是,通过 数据输入流选择单元和输出数据流选择单元,按照节拍,相互配合的切换,将经过的缓存数据流没有停顿时间地送到 数据流运算处理模块。

乒乓操作优点如下:

1、实现数据的无缝缓冲和处理,按照节拍配合。

2、节约缓冲区空间。

3、可实现低速模块处理高速模块(实质:通过DPRAM这种缓存单元实现数据流的串并转换)。

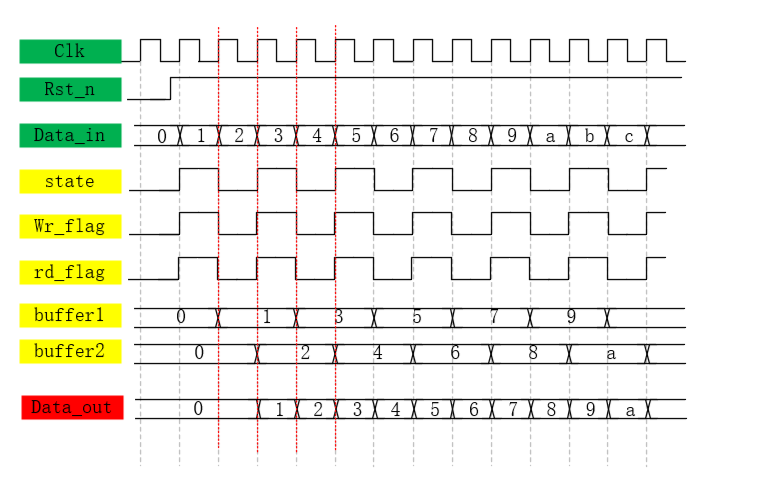

根据功能画出时序图:

代码实现:

1 module pingpang( 2 input wire clk , 3 input wire rst_n , 4 input wire [7:0] data_in , 5 output reg [7:0] data_out 6 ); 7 reg [7:0] buffer1; 8 reg [7:0] buffer2; 9 reg wr_flag; 10 reg rd_flag; 11 reg state ; 12 13 always@(posedge clk or negedge rst_n) 14 begin 15 if(rst_n==1'b0) 16 state<=1'b0; 17 else 18 state<=~state; 19 end 20 21 always@(*) 22 begin 23 case(state) 24 1'b0 : begin wr_flag<=0; rd_flag<=0; end 25 1'b1 : begin wr_flag<=1; rd_flag<=1; end 26 default : begin wr_flag<=0; rd_flag<=0; end 27 endcase 28 end 29 30 always@(posedge clk or negedge rst_n) 31 begin 32 if(rst_n==1'b0) 33 begin 34 buffer1<=8'b0; 35 buffer2<=8'b0; 36 end 37 else 38 begin 39 case(wr_flag) 40 0 : buffer2<=data_in; 41 1 : buffer1<=data_in; 42 default : begin buffer1<=8'b0; buffer2<=8'b0; end 43 endcase 44 end 45 end 46 47 48 always@(posedge clk or negedge rst_n) 49 begin 50 if(rst_n==1'b0) 51 data_out<=8'b0; 52 else 53 begin 54 case(rd_flag) 55 0 : data_out <= buffer1; 56 1 : data_out <= buffer2; 57 default : data_out<=8'b0; 58 endcase 59 end 60 end 61 62 endmodule 63

注 : state 控制两个缓冲器读写状态切换。wr_flag=1,buffer1 写;wr_flag=0,buffer2 写;rd_flag=0,buffer1 读;wr_flag=1,buffer2 读;

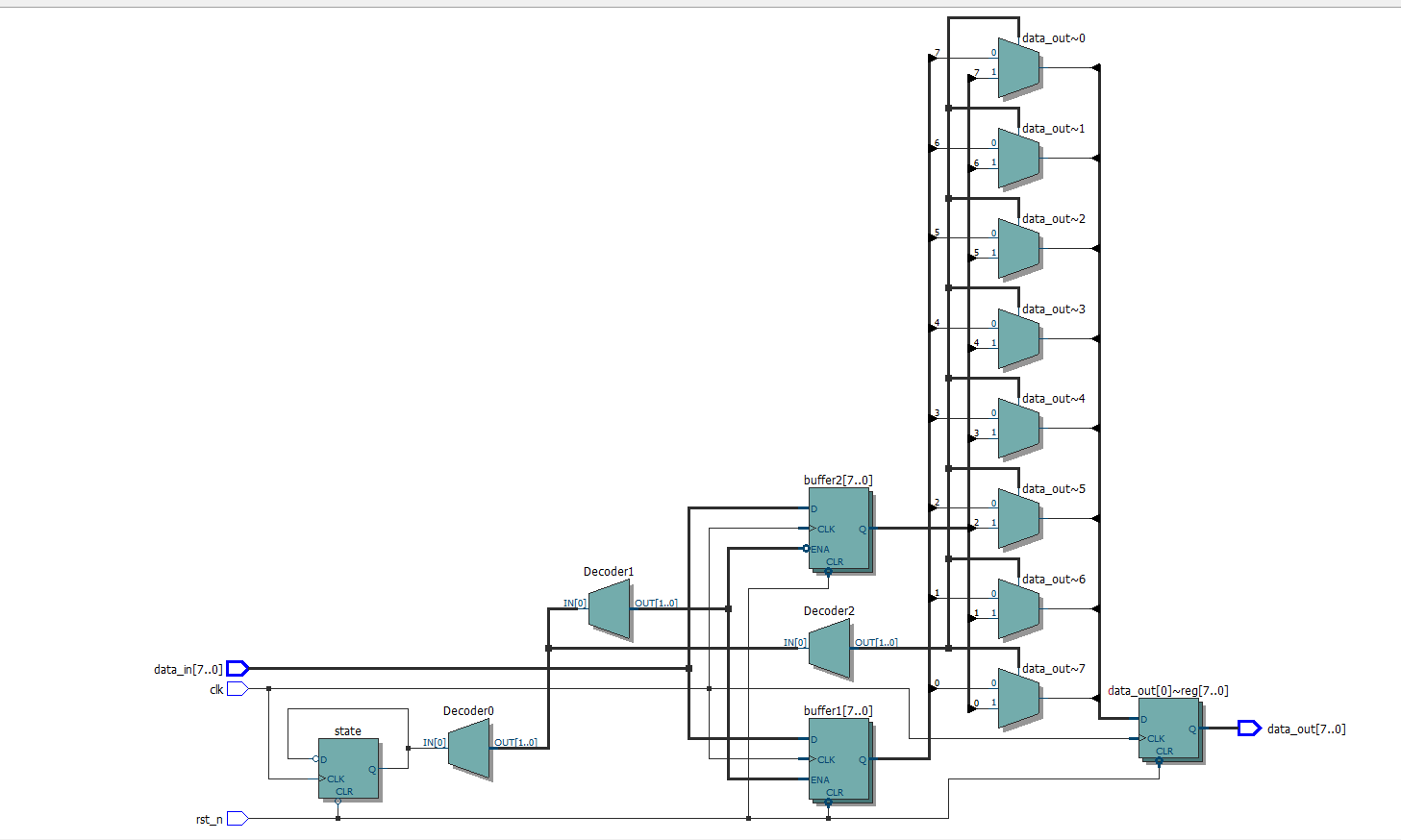

RTL视图:

测试代码:

1 `timescale 1ns/1ps 2 3 module tb_pingpang(); 4 reg clk ; 5 reg rst_n ; 6 reg [7:0] data_in ; 7 wire [7:0] data_out ; 8 9 initial 10 begin 11 clk = 0; 12 rst_n = 0; 13 #50 rst_n = 1; 14 #1000000 $finish; 15 end 16 17 always #10 clk=~clk; 18 19 always@(posedge clk or negedge rst_n) 20 begin 21 if(rst_n==1'b0) 22 data_in<=8'b0; 23 else 24 data_in<=data_in+1; 25 end 26 pingpang pinpang_inst 27 ( 28 .clk (clk) , 29 .rst_n (rst_n) , 30 .data_in (data_in) , 31 .data_out(data_out) 32 ); 33 34 endmodule

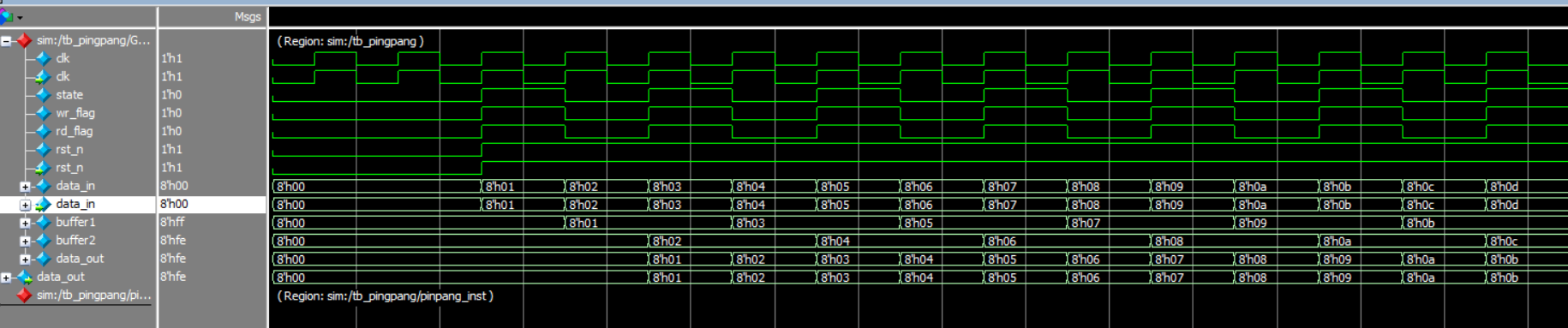

modelsim 仿真波形:

拓展: 也可以每个缓冲区后跟一个预处理模块,通过乒乓操作可以降低预处理模块的处理速率。如下图所示:

参考资料:

1、Intel FPGA/CPLD设计

2、(105条消息) FPGA设计——verilog实现乒乓操作并modelsim仿真_Fighting_XH的博客-CSDN博客_乒乓操作verilog

原文地址:http://www.cnblogs.com/yhm1314/p/16867575.html