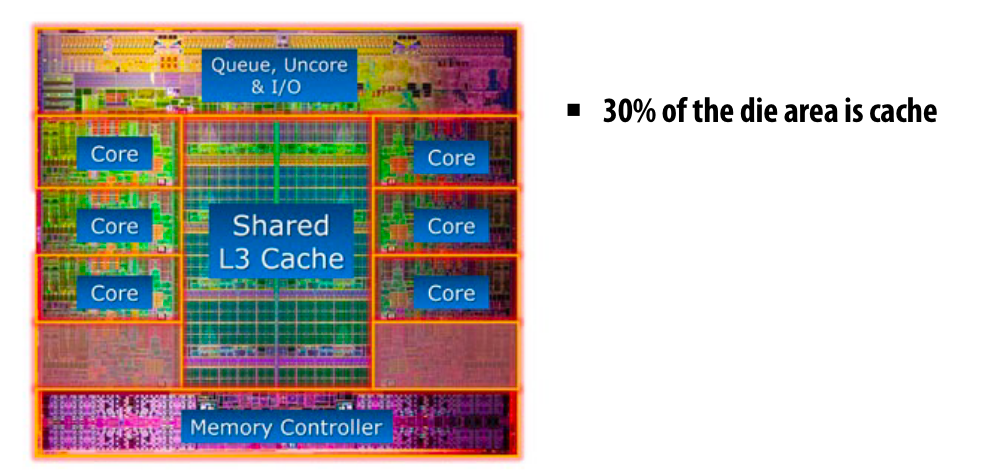

Cache一致性

关于Cache,我感觉通过这门课程学习到的内容可能还不够。我现在思考Cache读Memory有点像思考Memory读SSD。

- Cache每次都需要从Memory读64B,而内存读SSD每次都会读4KB

- 内存有带宽bandwidth,而SSD也有限制不过叫IOPS。

而且现在主要还都是再讲shared Memory的Cache一致性,我其实更想关注uniform Memory的Cache一致性。

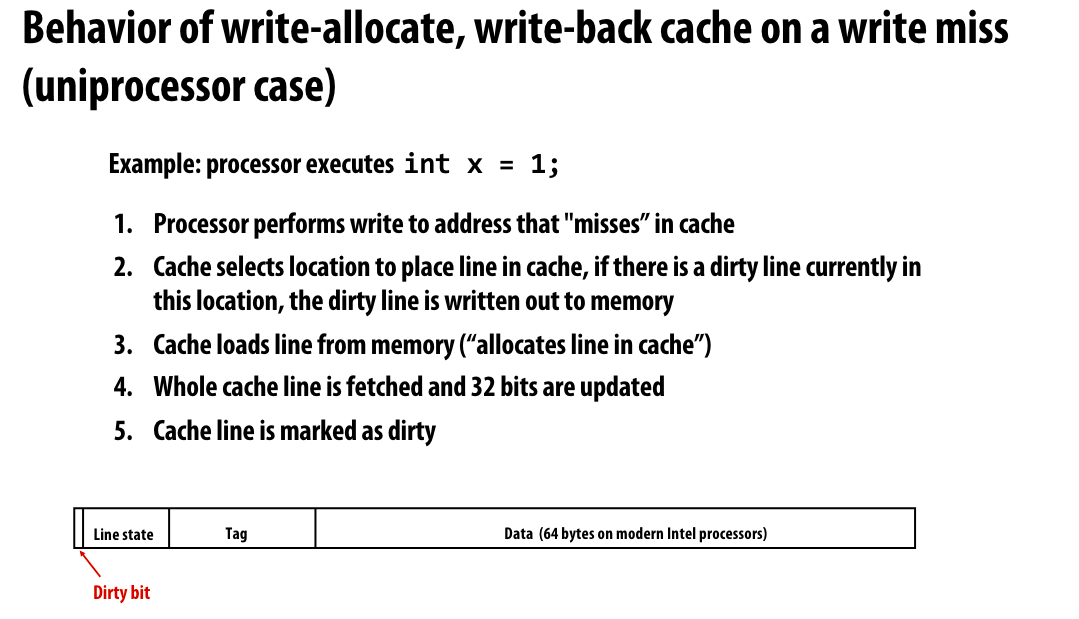

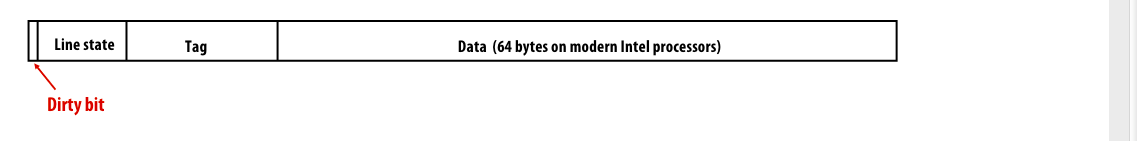

单核cpu的读写Cache

- Cache也有分为write though和write back,一般提到的都是write back

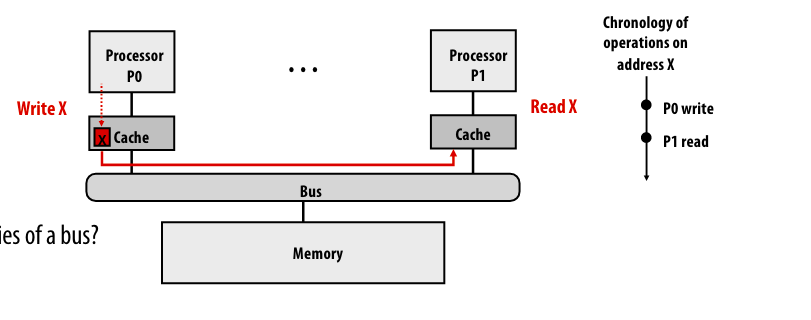

shared memory multo-processor

- 任何processor从address X处读取的value值应该是最近一次任意processor写的值

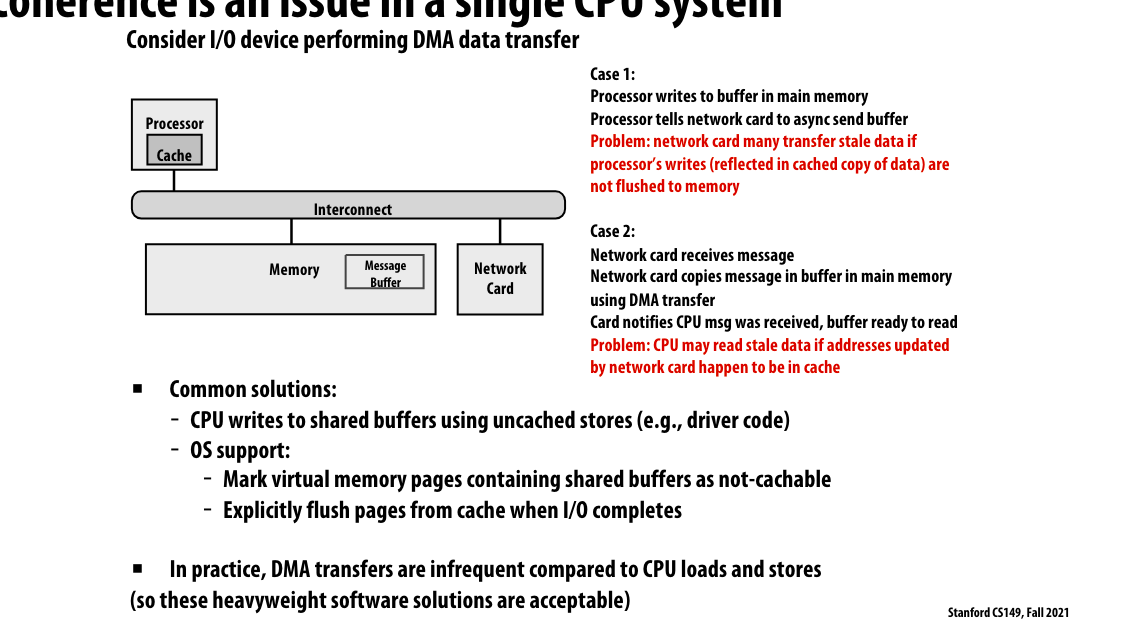

单核CPU系统的Cache一致性

即使是single cpu system也有可能出现Cache的不一致性。有可能DMA和network card向内存中写了数据,而CPU没有及时flush Cache就会出现不一致性。

解决办法

- OS直接将这个shared buffers的page标记为不可Cache

- 显式地flush Cache,当IO完成时

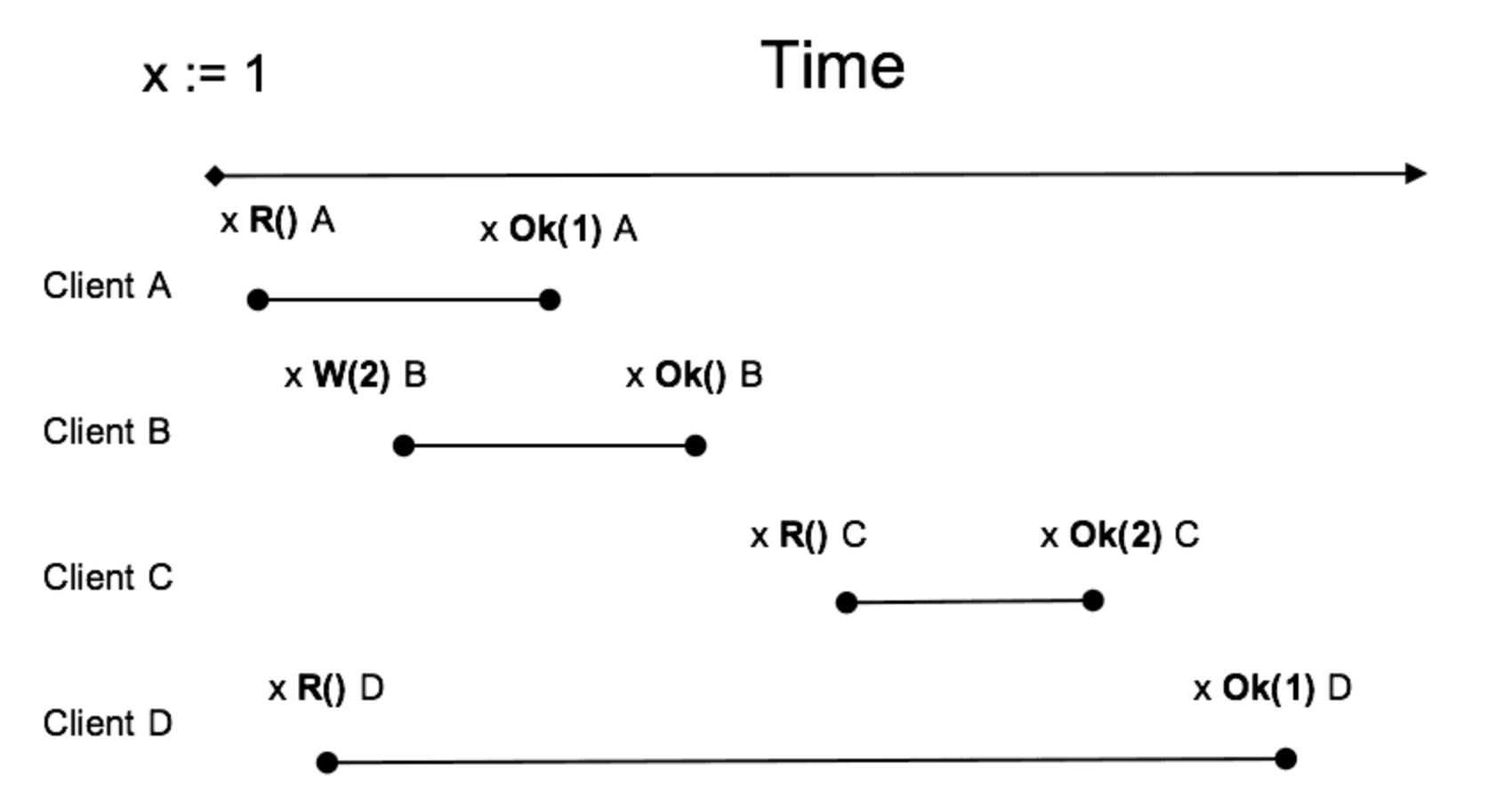

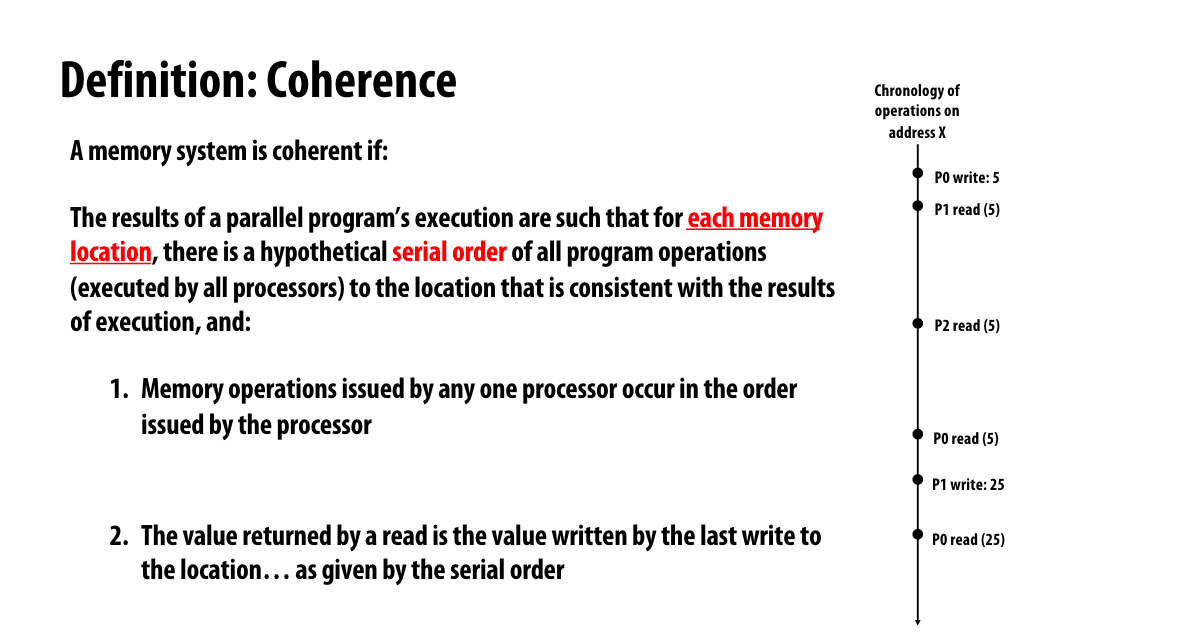

一致性定义

这里的一致性和我当时学操作系统这门课程接触到的一致性很像啊。

所以这里重温一下当时学的线性一致性:

client 发起请求也就是inv,client收到server的回复resp

背景知识介绍完了,怎样才能达到线性一致?这就要求 Server 在执行 Operations 时需要满足以下三点:

- 瞬间完成(或者原子性)

- 发生在 Inv 和 Resp 两个事件之间

- 反映出“最新”的值

这里的最新很有意思,因为操作时原子性的,那么client A读取x可能发生在client B写A之前也可能发生在之后。但是一致性语义的核心就是,一旦client A读取到了最新的write,那么发生在client A这次读操作的任意client读操作(也就是其他client发出inv在client A这次收到resp之后),一定可以会看到最新的值。

回到内存的一致性语义:

- 所有processor对于内存的并行操作,可以被序列化为一个processor的操作

- 单个processor的对内存的任何操作都是顺序的

- 读取操作返回的是该内存地址最近一次write的结果。

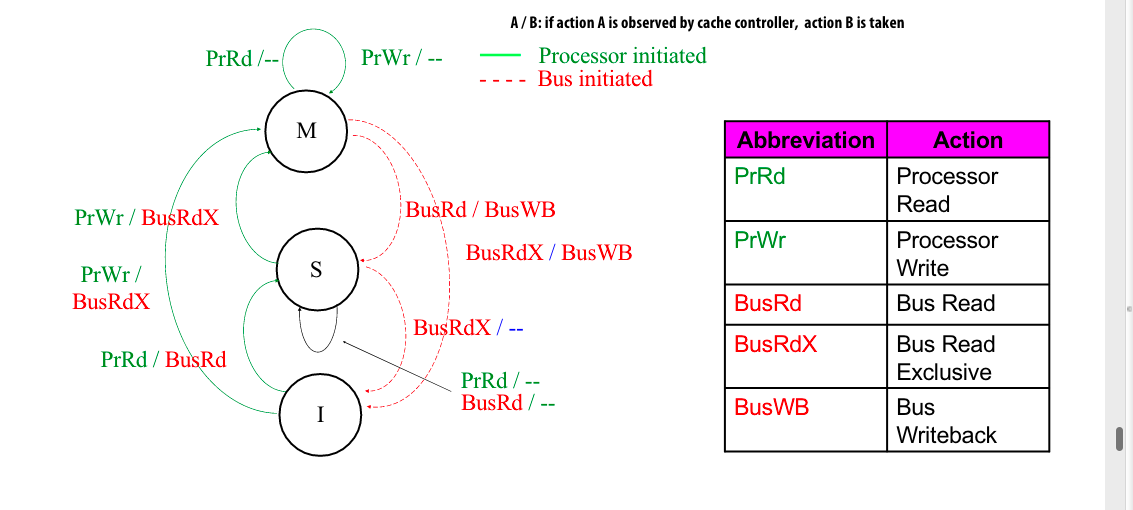

实现Cache一致性,这里教授主要讲了一种基于snoop的硬件实现算法:

可以用状态机描述Cache状态的变化

原文地址:http://www.cnblogs.com/kalicener/p/16926896.html

1. 本站所有资源来源于用户上传和网络,如有侵权请邮件联系站长!

2. 分享目的仅供大家学习和交流,请务用于商业用途!

3. 如果你也有好源码或者教程,可以到用户中心发布,分享有积分奖励和额外收入!

4. 本站提供的源码、模板、插件等等其他资源,都不包含技术服务请大家谅解!

5. 如有链接无法下载、失效或广告,请联系管理员处理!

6. 本站资源售价只是赞助,收取费用仅维持本站的日常运营所需!

7. 如遇到加密压缩包,默认解压密码为"gltf",如遇到无法解压的请联系管理员!

8. 因为资源和程序源码均为可复制品,所以不支持任何理由的退款兑现,请斟酌后支付下载

声明:如果标题没有注明"已测试"或者"测试可用"等字样的资源源码均未经过站长测试.特别注意没有标注的源码不保证任何可用性